# Name

Section

#### Purpose:

- \* To examine different types of bias used to set up a stable operating point.

- \* To sketch and label a DC load line for a transistor bias.

#### <u>Equipment</u>:

DMM

dc micro ammeter

dc voltmeter

dc Power Supply

Meter and Test Leads

Transistors - 2N3904 NPN (Q<sub>1</sub>, Q<sub>2</sub>, Q<sub>3</sub>)

Resistors ( 330 Ω, 1 kΩ, 2 kΩ, 10 kΩ, 680 kΩ )

#### Pre-lab Preparation:

- Review sections 7.1, 7.2, & 7.3 of Introductory Electronic Devices and Circuits

- Perform the dc analysis & complete the calculated portion of Tables 1 & 2.*Show all Calculations* - Find  $I_{C(sat)}$  &  $V_{CE(aff)}$  and plot the load line and plot the calculated Q point for both circuits.

#### Discussion: Base Bias

The transistor has three regions of operation ; saturation, active, and cutoff.

<u>*The saturation region*</u> is when the transistor is in its totally "on" state. It is acting like a closed switch, and the collector current is at its maximum.

<u>The cutoff region</u> is when the transistor is in its totally "off" state. It is acting like an open switch and the collector current is at its minimum. (It should be very close to zero).

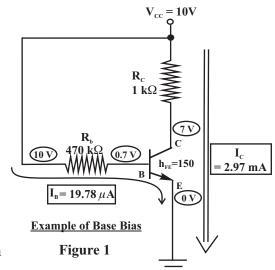

**The active region** is when the transistor is anywhere between saturation and cutoff. When it is in this region, the collector current is controlled by the base current. Remember that our transistor is basically a simple device. Look at Figure 1 to the right. It is an example of a **Base Bias** circuit. If we have a small amount of current flowing in the base circuit, we should have a larger current flowing in the collector circuit when the transistor is in the active region. The

ratio between these two currents is called the dc current gain of the transistor ( $h_{FE}$ ). In Fig. 1 the base current is 19.78  $\mu$ A. This base current is determined by the value of  $R_B$ . The collector current is 2.97 mA. This is determined by the dc current gain of this transistor. Since this transistor has a current gain of 150, the collector current  $I_c$ , is 150 times larger than the base current. If this transistor had a gain of less than 150, then  $I_c$  would also be less. Conversely, if this transistor had a gain of more than 150, then  $I_c$  would be higher. As you can see, for a base bias circuit,  $I_c$  can be different for each transistor. The 2N3904 used here can have a current gain of anywhere from 100 to 300. This means that  $I_c$  can vary widely depending on the transistor we use.  $I_c$  is considered to be unstable because it can vary widely with different transistors of the same type.

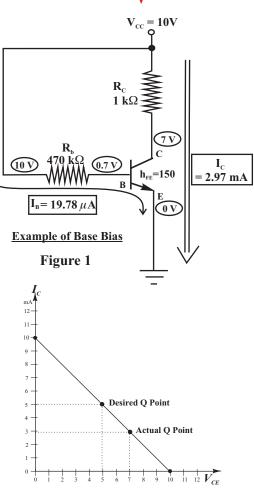

# The Q Point and Midpoint Bias

The Q point refers to the collector current. In the circuit shown in Fig. 1, the collector current is 2.97 mA. This is referred to as the Q point because the collector current will remain at 2.97 mA provided that no other voltages affect the circuit. In other words this means that a current of 2.97 mA will normally flow in the collector circuit with no signal applied. Our purpose here is to eventually use our transistor circuit as an amplifier. We need to have the Q point as close to the centre of the load line is possible. In the case in Fig. 1, the maximum collector current that can flow is 10 mA.( $I_{C(sat)}$ )This means the ideal Q point is at 5 mA. When the Q point is at 5 mA, the value of  $V_{CE}$  ( the voltage from collector to emitter) will be  $\frac{1}{2}$  of  $V_{CC}$  or 5 V. Note that this is also at the midpoint.

Look at Fig. 1. Is this particular circuit midpoint biased ? Your answer should be *no*. We have already determined that midpoint bias for this circuit is when the collector current is 5 mA and  $V_{CE}$  is 5 V ( $\frac{1}{2}$  V<sub>CC</sub>). The Q point for this circuit is *below the centre* of the load line at I<sub>C</sub> =2.97 mA and V<sub>CE</sub> = 7 V. See the load line shown below.

#### <u>A Stable Q Point – Why do we need it?</u>

It is important that our initial Q point be in the centre of the load line. If it is located higher up the load line, or lower down the load line, our signal output from the transistor will likely be distorted. The problem is that  $h_{FE}$  varies from transistor to transistor. Because

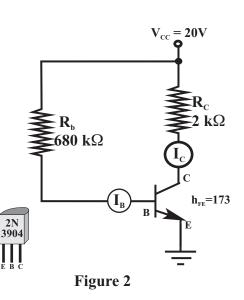

of this, our *Q* point is unpredictable if we use the <u>base bias</u> circuit shown in Fig. 1. Remember that our purpose is to consistently produce a Q point that is near the centre of the load line. The base bias circuit just doesn't do it. The reason is that the Q point is dependent on the value of  $h_{FE}$ . We will attempt to prove this point with the circuit shown in Figure 2.

#### <u>Base Bias</u>

#### Dc analysis Worksheet (Pre Lab)

Using example 7.3 in the textbook as a guide , calculate  $I_B$ ,  $I_{CQ}$ , and  $V_{CEQ}$  for the circuit shown in Figure 2. Insert your answers on the *Calculated Values* line in Table 1. <u>Show all Calculations</u>

DC Load Line for Figure 1

| Table 1 <u>Base Bias</u>           | I <sub>B</sub> | I <sub>cq</sub> | V <sub>ceq</sub> |

|------------------------------------|----------------|-----------------|------------------|

| Calculated Values                  |                |                 |                  |

| Measured Values for Q <sub>1</sub> |                |                 |                  |

| Measured Values for Q <sub>2</sub> |                |                 |                  |

| Measured Values for Q <sub>3</sub> |                |                 |                  |

#### Plot the load line for the base biased circuit shown in Figure 2 (Pre-Lab)

Find both ends of the load line, plot these values, then draw a straight line to join the points.

#### Find I<sub>C(sat)</sub>

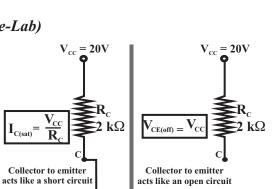

$I_{\rm C(sat)}$  is the maximum current that can flow when the transistor is saturated. This means that the transistor is acting like a closed switch as shown to the right. At this end of the load line,  $I_{\rm c}$  is at its maximum and  $V_{\rm CE}$  is near zero.

I<sub>C(sat)</sub>

$V_{CE(off)}$  is the voltage that appears across the transistor from collector to emitter when the transistor in acting like an open switch.  $V_{CE(off)}$  is  $V_{CC}$  when the transistor is in this region. The collector current is nearly zero when the transistor is in cutoff.

Plot the load line on graph to the right. Plot your calculated Q point on the graph and label it.

## **<u>Procedure:</u>** Do this part in the Lab

4 5 6 7 8 9 10 11 12 13 14 15 16 Load Line for Base Bias (Figure 2)

- 1) Build the circuit shown in Figure 2 on your breadboard.

- 2) Measure the value of  $I_B$ ,  $I_C$ , and  $V_{CE}$ . Record these values in Table 1 in the row for  $Q_1$ .

- 3) Repeat the above for  $Q_2$  and  $Q_3$ .

- Plot the measured Q points for all three transistors on the load line you created above. Label the Q points Q<sub>1</sub>, Q<sub>2</sub>, Q<sub>3</sub>

Finding the ends of the Load Line Figure 3

# Voltage Divider Bias

## **Discussion**

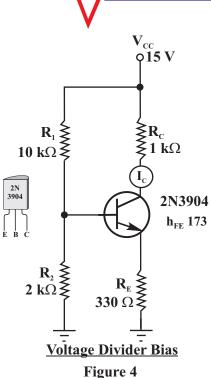

Voltage divider biased provides us with a much more Stable Q- point. With this type of bias, the  $h_{FE}$  of the transistor plays no part in determining the Q point. In this circuit, it is the *emitter resistor*  $R_E$  *that determines the collector current*.

This means that we can expect the Q-point to fall on the load line in the same place when we change the transistor to another of the same type. The following exercise will show this.

## Dc analysis worksheet (Pre-Lab)

Using example 7.11 in the textbook as a guide , calculate  $V_{\rm\scriptscriptstyle B}, V_{\rm\scriptscriptstyle E}, I_{\rm\scriptscriptstyle CQ}$ , and  $V_{\rm\scriptscriptstyle CEO}$  for the circuit shown in Figure 4.

Insert your answers on the *Calculated Values* line in Table 2.

#### Show all Calculations

| Table 2 VDB Bias                   | V <sub>B</sub> | V <sub>E</sub> | I <sub>cq</sub> | V <sub>ceq</sub> |

|------------------------------------|----------------|----------------|-----------------|------------------|

| Calculated Values                  |                |                |                 |                  |

| Measured Values for Q <sub>1</sub> |                |                |                 |                  |

| Measured Values for Q <sub>2</sub> |                |                |                 |                  |

| Measured Values for Q <sub>3</sub> |                |                |                 |                  |

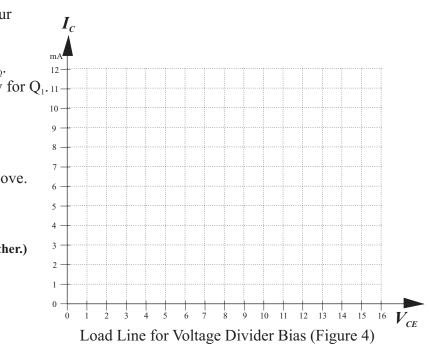

Plot the load line for the Voltage Divider Bias Circuit shown in Figure 4 (Pre-Lab)

1) Find both ends of the load line, plot these values, then draw a straight line to join the points.

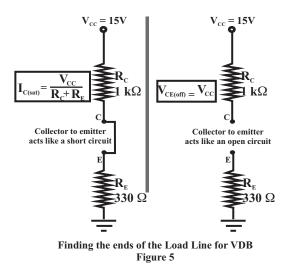

#### Find I<sub>C(sat)</sub>

$I_{\rm C(sat)}$  is the maximum current that can flow when the transistor is saturated. This means that the transistor is acting like a closed switch as shown to the right. At this end of the load line,  $I_{\rm C}$  is at its maximum and  $V_{\rm CE}$  is at zero. The current flowing in the circuit is determined by the total resistance in the circuit. Notice that this time, there are two resistors in the circuit. The total resistance is the addition of these.

I<sub>C(sat)</sub>

## Find $V_{CE(off)}$

$V_{CE(off)}$  is the voltage that appears across the transistor from collector to emitter when the transistor in acting like an open switch.  $V_{CE(off)}$  is  $V_{CC}$  when the transistor is in this region. The collector current is zero when the transistor is in cutoff.

V<sub>CE(off)</sub>

#### Plot the load line on graph below. Plot your calculated Q point on the graph and label it.

#### **<u>Procedure: Voltage Divider Bias</u> Do this part in the Lab**

- 1) Build the circuit shown in Figure 4 on your breadboard.

- 2) Measure the value of  $V_B$ ,  $V_{E_1}$ ,  $I_{CQ}$ , and  $V_{CEQ}$ . 12 Record these values in Table 2 in the row for  $Q_1$ .11

- 3) Repeat the above for  $Q_2$  and  $Q_3$ .

- 4) Plot the measured Q points for all three transistors on the load line you created above.

- 5) Label the Q points  $Q_1, Q_2, Q_3$ .

(The Q points should plot almost on top of each other.)